# A 4M Pixel CMOS Image Sensor for High Speed Image Capture

P. Donegan, E. Fox, B. Li, M. Sonder, F. Feng, M. Kiik, S. Xie DALSA Corp.

605 McMurray Rd. Waterloo Ontario Canada N2V 2E9 paul.donegan@dalsa.com

#### Abstract

This article describes a 4M pixel, 60 frame per second CMOS image sensor designed for high speed machine vision applications. The sensor employs a 5-transistor pixel and features snapshot image capture, electronic control. and simultaneous exposure integration and readout. The analog data is processed and digitized by two columnparallel signal chains, and the digitized data is routed through dual high speed column multiplexers to two differential output taps each ten bits wide and operating at a data rate of 160MHz.

### I. Introduction

There has been much development of CMOS image sensors for digital still photography, mobile applications, and other applications where the final image will be viewed by a human<sup>1-3</sup>. However. there has been comparatively little development of image sensors that are optimized for machine vision applications<sup>4,5</sup>. As a result, interline transfer (ILT) CCD technology has remained the image sensor technology of choice for cameras targeted to industrial applications such as electronics inspection, traffic inspection, and industrial metrology.

In this paper, we describe a 4 MPixel CMOS image sensor that has been developed specifically for machine vision applications and exceeds the performance achieved with comparable ILT CCD technology. The pixel architecture allows for global shuttering with electronic exposure control, and the signal chain is capable of reading the array at up to 60 frames per second.

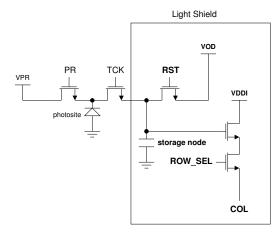

# II. Pixel Architecture

The pixel is based on a 5-transistor architecture as illustrated in Figure 1. Signal charge is collected on the photo site during the integration phase. Prior to integration PR is held high and photo charge is drained to VPR. Integration begins when PR is clocked to low and continues until the TCK gate is clocked high. Then, signal charge is spilled into the storage node. The TCK and PR gates are addressed globally. Charge in the sense node is converted to a voltage which is buffered onto the column signal bus on a row-wise basis and is sampled at the base of the column. Following each row read the storage nodes for the row are reset through the RST gates. The reset storage node levels are sampled. The two sampled levels are differenced in column-wise switched capacitor amplifiers in order to correct for offset differences in the pixel buffers and resistive voltage drops in the column buses.

This circuit topology allows for synchronous charge integration (no rolling shutter artifact) in conjunction with electronic exposure control (signal integration during a portion of the frame read out time) and with simultaneous image capture and frame readout (100% temporal coverage and maximum use of the available optical signal). There are other circuit topologies and clocking schemes that can be used to achieve the same combination of functionalities. For example, if a sixth transistor is added to the pixel then the photo charge can be sensed directly on the photo site as a voltage and buffered to an in-pixel sample-and-hold capacitor. This can be advantageous in terms of minimizing the contamination of the signal stored on the inpixel memory elements, however other considerations make this solution less favourable: fixed pattern noise (FPN) that cannot be easily differenced on-chip; reduced voltage swing in the pixel; higher temporal noise; and reduced fill factor. An alternative clocking of the 5T pixel eliminates the spill of signal charge from the photo site to the sense node but has higher reset noise. Similarly, a 4T pixel can be configured to operate with a synchronous shutter, however one needs to sacrifice either electronic exposure control or the ability to simultaneously integrate and readout.

Machine vision applications typically offer high illumination levels. The well capacity and photosensitive area per pixel therefore need to be larger than in most consumer image sensors. For a 4M pixel array, 7.4 µm is close to the maximum pixel pitch that can be accommodated in a single reticle field. The device described in this paper was targeted to a 0.25 um dual-oxide triple-metal fabrication process. The dual-oxide process allows for a higher voltage rail in the pixel array and in turn a larger well capacity. By optimizing both the absolute capacitances in the pixel as well as the capacitance ratio of the photo site to the sense node a full well capacity of the order of 70,000 electrons has been achieved. The use of 3 metals in conjunction with a microlens process allows for a reasonable compromise between high effective fill factor (~75%) and a low optical stack. The use of a deep pixel implant in conjunction with a shallow storage node implant has allowed us to achieve crosstalk levels between the photo site and the storage node that rival what is achieved in machine vision ILT devices.

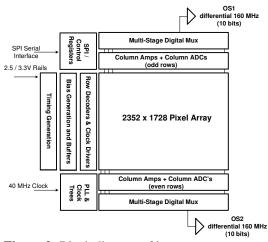

# III. Signal Chain Architecture

In order to achieve the target 60 Hz frame rate the data path needs to support an average throughput of 240 Mpixels/s and a burst rate of 320 Mpixels/s. A block diagram of the signal chain is illustrated in Figure 2. For each column in the pixel array there are two parallel analog chains. The chain at the bottom of each column processes even rows and the chain at the top of each column processes odd rows. This interleaved configuration is used to achieve maximum throughput independent of the vertical region of interest.

Each chain consists of a switched capacitor difference-and-hold preamplifier circuit followed by a 10 bit analog-to-digital converter (ADC). The ADCs are implemented in a single slope architecture which is driven by an 80 MHz on-chip ramp generator. The digital data is stored in a double buffered latch – while the data from one row is being processed by the ADC, the data from the previous row is being simultaneously read out through a high speed column multiplexer. The column multiplexers are configured as pipelined analog switch networks and are clocked at 160 MHz. The digital data from each chain (even rows and odd rows) is driven off-chip by differential drivers at 160 MHz per channel.

There are two programmable gain stages in the analog chain to provide a gain range from -3.0dB to 8.0dB. The first gain stage is in the preamplifier circuit, where one of four coarse gain settings is selected by switching in different feedback capacitors. The second gain stage provides fine resolution by adjusting the swing of the ramp signal used in the single slope ADC.

# **IV. Support Circuitry**

All clocks and biases are generated on-chip. A phase locked loop (PLL) is configured as a clock multiplier to allow high speed internal timing with a low frequency input clock. Region of Interest (ROI) control and digital timing are programmable to allow for higher frame readout speeds at lower resolution and for optimization of sensor performance. A serial-parallel interface provides access to the on-chip configuration registers.

The clock and bias networks were carefully designed to minimize image artifacts associated with high frame rate, large array size and snapshot imaging.

# V. Sensor Characterization

A preliminary characterization of the sensor has been performed. The results are shown in Table 1 for the nominal 0dB gain setting. Figure 6 shows a sample still image

Table 1: Sensor Performance Test Results

| Specification      | Value               | Unit                     |

|--------------------|---------------------|--------------------------|

| Saturation Level   | 1023                | DN                       |

| Saturation Level   | ~ 70                | ke                       |

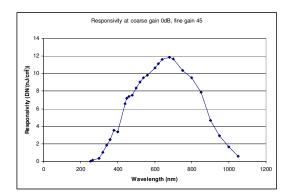

| Responsivity       | 11.8 <sup>(1)</sup> | DN/(nJ/cm <sup>2</sup> ) |

| Random noise       | 1.2                 | rms DN                   |

| Random noise       | 82                  | rms e <sup>-</sup>       |

| Dark Offset (2)    | 100                 | DN                       |

| Dynamic range      | 58.6                | dB                       |

| FPN <sup>(2)</sup> | 20.0                | DN rms                   |

| FPN <sup>(3)</sup> | 2.2                 | DN rms                   |

| PRNU               | 1-2                 | % rms                    |

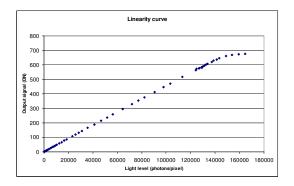

| Linearity          | 1 <sup>(4)</sup>    | %                        |

| Specification      | Value               | Unit            |

|--------------------|---------------------|-----------------|

| Power              | 1.5                 | W               |

| Antiblooming       | > 200x              | sat light level |

| Lag                | < 1                 | %               |

| Shutter Leakage    | 0.03 <sup>(5)</sup> | %               |

| MTF <sup>(6)</sup> | > 60                | %               |

<sup>(1)</sup> Peak, see Figure 3

<sup>(2)</sup> Electronic exposure control enabled

<sup>(3)</sup> Electronic exposure control disabled

<sup>(4)</sup> see graph in Figure 4

<sup>(5)</sup> white light source

<sup>(6)</sup> At 1.0 Nyquist and 550nm

#### VI. High Speed Image Capture Performance

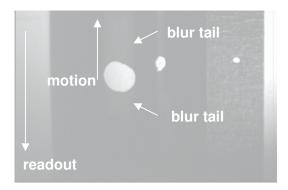

A critical performance metric for high speed imaging is shutter leakage. Shutter leakage is caused by intra-pixel crosstalk between the photo site and the storage node. In ILT CCD sensors intra-pixel crosstalk is manifested by smear. As the electronic signal is shifted down the vertical CCD, signal from the subsequent frame leaks into the vertical CCD thereby contaminating the vertical information content of the image. Advanced CCD ILT sensors typically achieve smear values in excess of 90 dB<sup>6</sup> which corresponds to crosstalk of less than 1 part in 3000. In CMOS sensors intra-pixel crosstalk also leads to image contamination, however the characteristics are different. For example, images from static scenes display no artifacts - crosstalk only influences images from dynamic scenes. And the crosstalk in dynamic scenes only affects the pixels along the trajectory of the object. In general far fewer pixels in an image captured by a CMOS stop-action sensor will be affected compared to the image captured by an ILT CCD. This can be a significant advantage in applications like electronics inspection and traffic inspection where the information content is generally in the regions away from the scene highlights.

An example of high speed image capture performed with the sensor described in this paper is illustrated in Fig. 5. The test conditions were designed to exaggerate the effects of intra-pixel crosstalk. The exposure time is 20  $\mu$ s and the frame time is 33 ms. The scene moves 0.4 frames between exposures. The large white spot in the lower

left quadrant has a blur tail that extends up by approximately 2 spot diameters and down by approximately 1 spot diameter. The signal level in the blur region is approximately 10% of the level in the dot. The corresponding crosstalk ratio is better than 1 part in 3,000.

#### **Conclusions:**

Design details and performance results have been presented for a CMOS image sensor designed for high speed machine vision applications. The sensor captures images with 4 Mpixel resolution at 60 fps.

#### ACKNOWLEDGEMENTS

We would like to thank Queintin Tang and Oscar Simioni for their assistance in developing the evaluation platform for measuring sensor performance.

#### REFERENCES

- T. Isogai, T. Ishida, A. Kamashita, S. Suzuki, M. Juen and T. Kazama, "4.1 Mega Pixel JFET Imaging Sensor LBCAST", Proc. of SPIE-IS&T Electronic Imaging, SPIE Vol. 5301, pp. 258 – 263, Jan. 16-20, 2005

- M. Kasano, Y. Inaba, M. Mori, S. Kasuga, T. Murata and Y. Yamaguchi, "A 2.0 um Pixel-Pitch MOS Image Sensor With an Amorphous Si Film Color Filter", 2005 IEEE Solid State Circuits Conference, Feb. 6-10, San Francisco, USA

- H. Takahashi, M. Kinoshita, K. Morita, T. Shirai, T. Sato, T. Kimura, H. Yuzurihara and S. Inoue, "A 3.9 mm Pixel Pitch VGA Format 10b CMOS Image Sensor with 1.5-Transistor Pixel", 2004 IEEE Solid State Circuits Conference, Feb. 15-19, San Francisco, USA

- E.C. Fox, G.R. Allan, B.Li, D. Dattani, S. Kamasz, M.J. Kiik, Q. Tang, A. Pavlov, D. Dykaar, S.G. Ingram, "A 640x480 CMOS Image Sensor for High Speed Image Capture", 2001 IEEE Workshop on Charge-Coupled Devices and Advanced Image Sensors, Jun 7-9, 2003, Lake Tahoe, USA

- H. Witters, T. Walschap, G. Vanstraelen, G. Chapinal, G. Meynants, B. Dierickx, "1024 x 1280 Pixel Dual Shutter APS for Industrial Vision", Proc. of SPIE-IS&T Electronic Imaging, SPIE Vol. 5017, Jan 20-24, 2003

- T. Yamada, H. Tanaka, K. Henmi, M. Kobayashi, H. Mori, Y. Katoh and Y. Miyata, "Improvement of Photo-Sensitivity and Smear Characteristics in a 2.8 um-square pixel IT-CCD Image Sensor", 2003 IEEE Workshop on Charge-Coupled Devices and Advanced Image Sensors, May 15-17, 2003, Elmau, Germany

Figure 1: Schematic of 5-transistor pixel.

Figure 2: Block diagram of image sensor

Figure 3: Spectral response curve

**Figure 4:** Output Linearity at minimum sensor gain, showing the pixel saturation level. The nominal gain setting is defined such that the analog chain and output saturate with the pixel.

**Figure 5:** Example of high speed image capture. The exposure time is 20  $\mu$ s and the frame time is 33 ms. The scene moves 0.4 frames between exposures. The signal magnitude in the blur tail is approximately 10% of the signal level in the dot.

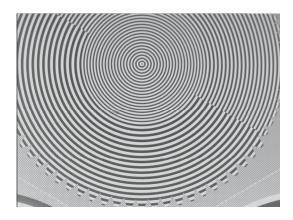

Figure 6: Sample Still Image