#### **Features**

f<sub>s</sub>: max 160 MHz

BW: 1 kHz - ½ f<sub>s</sub>

• noise (1 kHz - 20 MHz): -72 dBV

THD: -61 dBc

area: 0.1 mm²

• technology: 65 nm CMOS

•

## **Applications**

- I Baseband signal generation

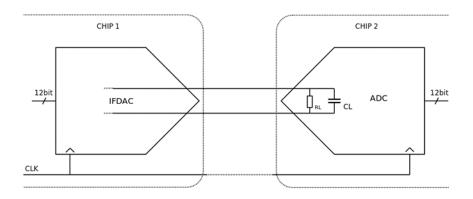

- Inter-chip data communication

- Video baseband transmitting

### **General description**

The CRDAC12b is a 12-bit charge-redistribution DAC.

The DAC is especially suited to discrete-time applications, where the output signal is sampled, but also works well in continuous-time applications.

The DAC has been optimized for high speed and low area. It has been designed for applications where DC transfer is not required.

#### This product is silicon verified

This product is still in development and all information in this datasheet is preliminary and subject to change

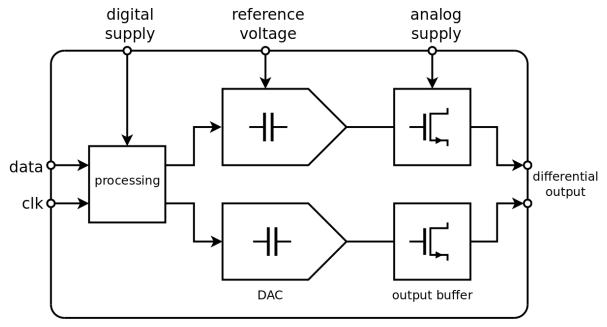

# **Block diagram**

Figure 1: Block diagram

CRDAC 12b – Revision F3 Page 1 of 7

# CRDAC 12b

#### **Ports list**

| Port name                         | Width | Description                             |  |  |

|-----------------------------------|-------|-----------------------------------------|--|--|

| Power, ground and reference ports |       |                                         |  |  |

| V <sub>dda</sub> 18               | 1     | 1.8 V analog supply voltage for buffers |  |  |

| V <sub>ref</sub> 12               | 1     | 1.2 V reference (supply) voltage        |  |  |

| V <sub>ddd</sub> 12               | 1     | 1.2 V digital supply voltage            |  |  |

| Gnd                               | 1     | Common ground                           |  |  |

| Analog outputs                    |       |                                         |  |  |

| Outp                              | 1     | Positive DAC output                     |  |  |

| Outn                              | 1     | Negative DAC output                     |  |  |

| Inputs (data and clock)           |       |                                         |  |  |

| Вх                                | 12    | Input data 12 bits                      |  |  |

| Clk                               | 1     | Clock input                             |  |  |

Table 1: port function description

CRDAC 12b – Revision F3 Page 2 of 7

# CRDAC 12b

12 bit charge-redistribution DAC

## **Specifications**

#### **Default test conditions**

Digital supply voltage (V<sub>ddd</sub>) 1.2 V Analog supply voltage (V<sub>dda</sub>) 1.8 V IO supply voltage (V<sub>ddio</sub>)<sup>1</sup> 1.8 V Reference voltage (V<sub>ref</sub>) 1.2 V Clock frequency (fclk) 160 MHz

Input signal frequency

Sampled-time measurements

Continuous-time measurements

Input signal amplitude

Load impedance

Ambient temperature (T)

5 MHz 0 dBFS

55 MHz

$2 k\Omega // 5 pF$  (differential)

25 °C

## **Specifications**

| Parameter          | Description                | Min | Тур  | Max | Units |

|--------------------|----------------------------|-----|------|-----|-------|

| fs                 | Sample rate                |     | 160  |     | MHz   |

| f <sub>clk</sub>   | Clock frequency            |     | fs   |     |       |

| V <sub>ddd</sub>   | Digital supply voltage     |     | 1.2  |     | ٧     |

| V <sub>dda</sub>   | Analog supply voltage      |     | 1.8  |     | ٧     |

| Vref               | Reference voltage          |     | 1.2  |     | V     |

| N                  | Input data width           |     | 12   |     | bits  |

| DC characteristics |                            |     |      |     |       |

| V <sub>cm</sub>    | Common mode output voltage |     | 0.6  |     | ٧     |

| I <sub>ddd</sub>   | Digital supply current     |     | <0.1 |     | mA    |

| I <sub>dda</sub>   | Analog supply current      |     | 14.9 |     | mA    |

| I <sub>ref</sub>   | Reference supply current   |     | 0.1  |     | mA    |

## **Specifications (continued)**

| Parameter      | Description                                                                                                                                    |                  | Тур        | Max      | Units |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|----------|-------|--|--|

| AC Performa    | AC Performance                                                                                                                                 |                  |            |          |       |  |  |

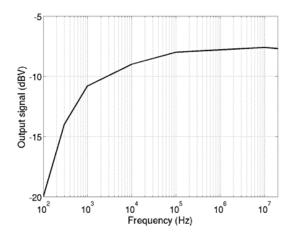

| Vout           | Output signal amplitude V <sub>in</sub> = 0 dBFS                                                                                               |                  | -7.4       |          | dBV   |  |  |

| BW             | Input signal bandwidth <sup>3</sup> (ADC has high-<br>pass transfer)<br>Sampled-time measurements <sup>4</sup><br>Continuous-time measurements | 10 <sup>-3</sup> |            | 60<br>20 | MHz   |  |  |

| Rout           | Output resistance                                                                                                                              |                  | 140        |          | Ω     |  |  |

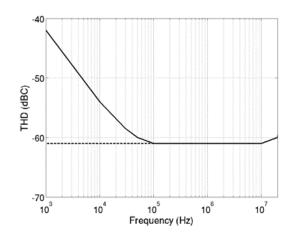

| THD            | Total harmonic distortion V <sub>in</sub> = 0 dBFS <sup>2</sup> Sampled-time measurement <sup>4</sup> Continuous-time measurement              |                  | -61<br>-61 |          | dBc   |  |  |

| N              | Noise floor 1 kHz-80 MHz, V <sub>in</sub> = -48 dBFS Sampled-time measurement <sup>4</sup> Continuous-time measurement                         |                  | -72<br>-72 |          | dBV   |  |  |

| Implementation |                                                                                                                                                |                  |            |          |       |  |  |

| Α              | Chip area in 65nm CMOS 0.1                                                                                                                     |                  | mm²        |          |       |  |  |

Table 2: Specifications

#### Notes:

- 1. The test chip uses LVDS I/O signals, therefore an additional supply, Vddio (1.8V), is implemented on the test chip.

- 2. THD degrades with smaller input signals, due to crosstalk in test chip; see Figure 2.

- 3. See Figure 3.

- 4. Extracted from simulation

CRDAC 12b – Revision F3 Page 4 of 7

## **Typical Performance Characteristics**

#### THD vs frequency

Figure 2: THD as function of frequency,  $V_{in} = 0$  dBFS (the increase in THD for low frequencies is due to cross talk in the test chip; the dotted line indicates expected THD after resolving this issue)

#### Amplitude vs frequency

Figure 3: DAC output amplitude as function of frequency (Vin = 0 dBFS)

CRDAC 12b – Revision F3 Page 5 of 7

## **Typical Applications**

Figure 4: Typical IFDAC data communication application

## **Deliverables**

The product can be delivered as a single IP component for customer integration or Axiom IC engineers can integrate the product as part of a SoC engagement.

# **Revision history**

| Revision | Date       | Reason for revision          |

|----------|------------|------------------------------|

| F1       | 2011-07-05 | Initial release              |

| F2       | 2012-06-26 | Removed "preliminary" status |

| F3       | 2017-07-20 | Updated template             |

Table 3: Document revision history

CRDAC 12b – Revision F3 Page 6 of 7

# For more information about Teledyne DALSA visit our Web Site at

http://www.teledynedalsa.com/semi/mixed-signal/

or contact us at

Teledyne DALSA Enschede

Colosseum 28

7521 PT Enschede

the Netherlands

+31 (0)53-7990700

info.enschede@teledyne.com

Information relating to products and circuits furnished herein by Teledyne DALSA B.V. or its subsidiaries ("Teledyne DALSA") is believed to be reliable. However, Teledyne DALSA assumes no liability for errors that may appear in this document, or for liability otherwise arising from the application or use of any such information which may result from such application or use. The products, their specifications and the information appearing in the document are subject to change by Teledyne DALSA without notice. Trademarks and registered trademarks are the property of their respective owners.

© 2018 Teledyne DALSA B.V. - All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE

CRDAC 12b – Revision F3 Page 7 of 7