#### Features

- sample-rate up to 12.5 MS/s

- low power consumption, proportional to sample-rate:

1.2 mW @ 12.5 MS/s

12 µW @ 125 kS/s

- single-ended and differential mode

- 10.5 ENOB

- >78 dB SFDR (incl. THD)

- 0.17 mm<sup>2</sup> in baseline 0.18 µm CMOS

- rail-to-rail input range

- supports full Nyquist band

- silicon proven

## **Applications**

- low-power applications

- sensor applications

- radio baseband processing

### General description

This datasheet describes a general purpose Analog to Digital Converter (ADC) for low-power applications. The converter is a charge-redistribution successiveapproximation type converter, suitable for the entire Nyquist band.

The key feature of this ADC is its low power consumption. This is achieved by using an energy efficient comparator and by making all circuitry dynamic. As a result, quiescent current in e.g. amplifiers is avoided, and the power consumption is fully proportional to the sample-rate. This property makes the ADC ideal for low duty-cycle sensor applications and other applications benefiting from low power consumption.

The converter can operate in both single-ended and differential mode, making it suitable for a broad range of applications.

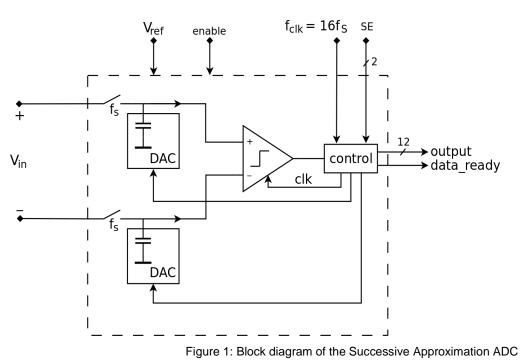

The functional block diagram is shown in Figure 1.

The IP product described in this datasheet is silicon proven.

Block diagram

Succesive approximation ADC

## Specifications

#### **Default test conditions**

| Supply voltage (VDD)                         | 1.8 V                                |

|----------------------------------------------|--------------------------------------|

| Reference voltage (VREF)                     | 1.0 V                                |

| Clock frequency (f <sub>CLK</sub> )          | 200 MHz (ADC sample-rate: 12.5 MS/s) |

| Common-mode input voltage (V <sub>CM</sub> ) | 0.5 V                                |

| Temperature (T)                              | 25 °C                                |

| -  ······                                    |                                      |

#### **Electrical Specifications**

| Parameter        | Description                                                                                                                                             | Min  | Тур   | Мах             | Units              |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------|--------------------|

| f <sub>S</sub>   | Sample-rate                                                                                                                                             | 0    |       | 12.5            | MS/s               |

| fclk             | Clock frequency                                                                                                                                         |      | 16    |                 | fs                 |

| V <sub>DD</sub>  | Supply voltage                                                                                                                                          | 1.65 | 1.8   | 1.95            | V                  |

| V <sub>REF</sub> | Reference voltage (without using reference buffer)                                                                                                      | 0.8  | 1     | V <sub>DD</sub> | V                  |

| V <sub>FS</sub>  | Full scale input voltage (single-ended)                                                                                                                 |      | 0.92  | 1               | VREF               |

| CIN              | Input capacitance (single-ended)<br>This includes about 1 pF bondpad capacitance. If the ADC is<br>integrated in a SoC this is reduced to about 0.2 pF. |      | 2     |                 | pF                 |

| lin              | Input current (single-ended)<br>(e.g. 0.7 µA for a sample-rate of 10 MS/s)                                                                              |      | 0.08  |                 | μΑ /<br>(MS/s)     |

| PADC             | Power consumption ADC at 12.5 MHz ( $f_{IN}$ = 0.6 MHz)                                                                                                 |      | 1.2   |                 | mW                 |

| PBUFFER          | Reference buffer <sup>1)</sup>                                                                                                                          |      | 790   |                 | μW                 |

| Performance      |                                                                                                                                                         |      |       |                 |                    |

| SFDR             | Spurious Free Dynamic Range<br>(f <sub>IN</sub> = 0.6 MHz) (including harmonics)                                                                        |      | 78    |                 | dB                 |

| SNR              | Signal to Noise Ratio<br>(V <sub>IN</sub> = 0 dB <sub>FS</sub> , f <sub>IN</sub> = 1.1 kHz)                                                             | 66   |       |                 | dB                 |

| ENOB             | Effective Number Of Bits (f <sub>IN</sub> = 1.1 kHz)                                                                                                    | 10.5 |       | bits            |                    |

| FoM              | Figure of Merit defined as: $\frac{P}{2^{ENOB} \cdot f_S}$                                                                                              |      | 0.07  |                 | pJ / conv.<br>step |

| DNL              | Differential Non-Linearity                                                                                                                              |      | ± 1.5 |                 | LSB                |

| INL              | Integral Non-Linearity                                                                                                                                  |      | ± 2   |                 | LSB                |

| Implementation   | on                                                                                                                                                      |      |       |                 |                    |

| Area             | Die area in 0.18 µm CMOS                                                                                                                                |      | 0.17  |                 | mm <sup>2</sup>    |

Table 1: Specifications of the Analog-to-Digital Converter

Notes: 1) A reference buffer is included on the test chip, which is available as a separate

IP block, see section Options.

Succesive approximation ADC

### Port list

| Port name  | Width                                                        | Description                                                                                                                                                                    |

|------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND        | 1                                                            | Ground                                                                                                                                                                         |

| VDD        | 1                                                            | Supply voltage                                                                                                                                                                 |

| VREF       | REF 1 Reference voltage, loaded with switched capacitor circ |                                                                                                                                                                                |

| CLK        | 1                                                            | Clock signal at 16.fs                                                                                                                                                          |

| ENABLE     | ENABLE 1 Enable signal for the converter (active high)       |                                                                                                                                                                                |

| VINP       | 1                                                            | Non-inverting analog input signal                                                                                                                                              |

| VINN       | 1                                                            | Inverting analog input signal                                                                                                                                                  |

| PSE        | 1                                                            | Selects VINN as single-ended input (active high). VINP must<br>be connected to ground externally. If both PSE and NSE are<br>low, VINP and VINN act as a differential input.   |

| NSE        | 1                                                            | Selects VINP as single-ended input (active high). VINN must<br>be connected to ground externally. When both PSE and NSE<br>are low, VINP and VINN act as a differential input. |

| OUT        | 12                                                           | Digital output signal, non-inverting, unsigned binary                                                                                                                          |

| DATA_READY | 1                                                            | Indicates that the conversion is complete and the output is<br>updated. This signal can be used to re-clock the output data.<br>(active high)                                  |

Table 2: port function description

# **Detailed description**

The SE signals select which of the two inputs ( $V_{INP}$  or  $V_{INN}$ ) is used as the single-ended input; the other input should be grounded. If both SE signals are zero, the converter operates in differential mode.

After the enable signal is made active high, the ADC will track the input signal at the next rising edge of clk, as indicated in Figure 2. At the next rising edge of clk, the input signal is sampled and the conversion is started. After finishing the conversion, the output code is updated and the data\_ready signal is activated. This signal can be used to re-clock the output data.

The ADC core requires a clock frequency ( $f_{CLK}$ ) of 16•f<sub>S</sub> and a buffered reference voltage ( $V_{REF}$ ) that is able to drive a switched capacitor network. The capacitance of this network is around 1 pF. This buffered voltage can either be made by an on-chip reference buffer, or it can be applied externally. In case  $V_{DD}$  is sufficiently clean, it can also be used as the buffered reference voltage. The reference voltage determines the full-scale voltage of the ADC.

Basically, the input impedance is purely capacitive, since at the end of the conversion, the charge on the capacitors is restored before the sample-switches are re-activated. Due to parasitic capacitance a small DC current (proportional to the sample frequency) will flow into the input nodes.

| clk                  |  |           |   | www                  |    |

|----------------------|--|-----------|---|----------------------|----|

| enable               |  | <br> <br> |   |                      |    |

| track (ADC internal) |  | <u>л</u>  | ſ | ſ                    |    |

| data_ready           |  |           |   |                      |    |

| data_out<11:0>       |  | X         | Х | X First valid sample | _X |

Figure 2: Timing diagram of the ADC

## Deliverables

The IP deliverables consist of a GDS file, a behavioral model, a netlist and integration documentation. The product can be delivered as a single IP component for customer integration or Axiom IC engineers can integrate the product as part of a SoC engagement.

## **Options**

For generating the buffered reference voltage, Axiom IC offers energy-efficient reference buffers specifically aimed at this converter and adjustable to the customer's requirements.

The converter can also be extended with gain and/or offset calibration.

For more information about these options, please contact us at info.enschede@teledyne.com.

## **Revision history**

The following table lists the revision history, only major revisions are shown.

| Revision | Date       | Reason for revision                                               |  |

|----------|------------|-------------------------------------------------------------------|--|

| F2       | 2017-07-18 | Template update                                                   |  |

| F1       | 2012-03-22 | First version of 12.5 MS/s variant, derived from SAADC 10MS/s 12b |  |

Table 3: Document revision history

# For more information about Teledyne DALSA visit our Web Site at

http://www.teledynedalsa.com/semi/mixed-signal/

or contact us at

Teledyne DALSA Enschede Colosseum 28 7521 PT Enschede the Netherlands +31 (0)53-7990700 info.enschede@teledyne.com

Information relating to products and circuits furnished herein by Teledyne DALSA B.V. or its subsidiaries ("Teledyne DALSA") is believed to be reliable. However, Teledyne DALSA assumes no liability for errors that may appear in this document, or for liability otherwise arising from the application or use of any such information which may result from such application or use. The products, their specifications and the information appearing in the document are subject to change by Teledyne DALSA without notice. Trademarks and registered trademarks are the property of their respective owners.

© 2018 Teledyne DALSA B.V. - All Rights Reserved.

**TECHNICAL DOCUMENTATION - NOT FOR RESALE**